Key Takeaways

- Analog compute-in-memory architectures eliminate the energy-intensive movement of data found in traditional digital processors.

- By utilizing variable electrical currents rather than binary switching, these chips can deliver massive efficiency gains for edge AI.

- The technology addresses the critical "memory wall" bottleneck, though it faces significant hurdles regarding software toolchains and signal noise.

For the last decade, the race in artificial intelligence processors has been defined by a brute-force philosophy: bigger dies, higher clock speeds, and massive power envelopes. But as AI models grow exponentially larger, that approach is hitting physical and thermal walls.

This reality has carved out a niche for a different kind of architecture. Players in the semiconductor market are betting that the path forward isn't about refining digital logic, but abandoning it entirely for specific tasks. This approach relies on analog chips, which use far less power than digital counterparts—a shift that could fundamentally change the economics of edge computing.

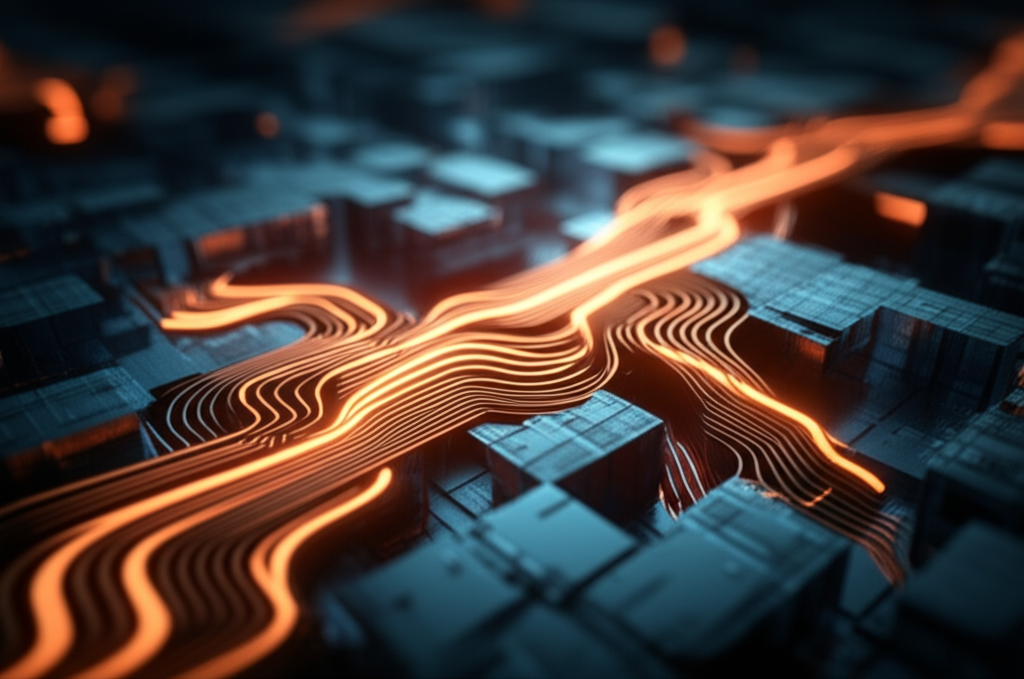

To understand why this matters, you have to look at the inefficiency inherent in the current standard. In a traditional digital system (like a GPU or CPU), the processor and the memory are separate. To perform a calculation, the chip must fetch data from memory, move it to the processor, do the math, and send it back.

It’s a small detail, but it tells you a lot about the current hardware crisis: moving that data actually consumes significantly more energy than the calculation itself. This is often called the "von Neumann bottleneck."

Analog AI processors bypass this by performing compute-in-memory. Instead of representing information as 0s and 1s that have to be shuttled back and forth, they use memory cells—often flash memory or similar resistive technologies—to store the weights of a neural network. By passing a current through these cells, the chip performs matrix multiplication (the core math of AI) instantly using Ohm’s Law.

The input is voltage, the weight is conductance, and the output is current. No data movement required.

The Efficiency Equation

Analog chips use drastically less power than digital options. In the context of a data center, that means lower electricity bills. But the real implications are at the edge.

Consider a security camera running complex object detection, or a drone navigating a warehouse. These devices are constrained by battery life and thermal limits. A high-powered digital GPU is often a non-starter because it drains the battery in minutes or requires a cooling fan that adds weight and mechanical failure points.

Analog processing promises to deliver high-performance inference within a fraction of the power budget. It allows sophisticated models—not just simple keyword spotting, but full vision transformers or large language models—to run on devices that previously couldn’t handle them.

Precision vs. Power

Still, the transition to analog isn't a simple swap. Digital logic is deterministic and precise; a 1 is always a 1. Analog signals are subject to noise, temperature fluctuations, and process variations.

That’s where it gets tricky for engineering teams. The challenge for companies in this space isn't just building the chip; it's building the compensation software that allows neural networks—which are surprisingly resilient to minor errors—to function correctly despite the inherent "fuzziness" of analog circuits.

Most AI inference doesn't actually require the extreme floating-point precision of a supercomputer. A neural network determining if a pedestrian is crossing the street needs to be accurate, but it doesn't need to calculate that probability to the fifteenth decimal point. Analog chips exploit this tolerance, trading a small amount of mathematical precision for massive gains in energy efficiency.

The Ecosystem Gap

What does that mean for teams already struggling with integration debt? It means the hardware is only half the story. The success of analog AI depends heavily on the software stack. Developers are accustomed to mature digital toolchains like CUDA. For analog chips to gain traction in B2B applications, the compilation software must be robust enough to abstract away the physical complexities of the chip. You can't ask a Python developer to understand the voltage variance of a flash cell.

The market for these processors is heating up precisely because the digital roadmap is showing diminishing returns. Moore’s Law is slowing down, but the demand for AI compute is accelerating.

For technical leaders and hardware architects, the emergence of viable analog options signals a divergence in the infrastructure. Training massive models will likely remain the domain of high-precision digital supercomputers. However, inference—the actual application of that intelligence in the real world—is increasingly looking for a lower-power home.

If the technology continues to mature, we may see a bifurcation in the industry: digital for learning, and analog for doing. The energy savings are simply too large for the market to ignore.

⬇️

⬇️